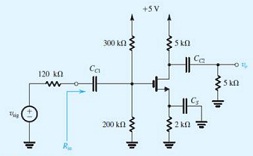

Response to the following problem:

The NMOS transistor in the CS amplifier shown in Fig. has Vt = 0.7 V and VA = 50 V.

(a) Neglecting the Early effect, verify that the MOSFET is operating in saturation with ID =0.5 Ma and VOV =0.3 V. What must the MOSFET's kn be? What is the dc voltage at the drain?

(b) Find Rin and Gv .

(c) If vsig is a sinusoid with a peak amplitude vˆsig, find the maximum allowable value of vˆsig for which the transistor remains in saturation. What is the corresponding amplitude of the output voltage?

(d) What is the value of resistance Rs that needs to be inserted in series with capacitor CS in order to allow us to double the input signal vˆsig ? What output voltage now results?