Discuss the below in detail:

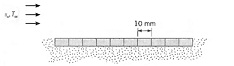

Q: An array of 10 silicon chips, each of length L = 10 mm on a side, is insulated on one surface and cooled on the opposite surface by atmospheric air in parallel flow with T8 = 24°C and U8 = 40 m/s. When in use, the same electrical power is dissipated in each chip, maintaining a uniform heat flux over the entire cooled surface.

If the temperature of each chip may not exceed 80°C, what is the maximum allowable power per chip? What is the maximum allowable power if a turbulence promoter is used to trip the boundary layer at the leading edge? Would it be preferable to orient the array normal, instead of parallel, to the airflow?