Response to the following problem:

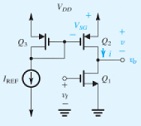

It is required to design the CMOS amplifier of Fig. utilizing a 0.18-μm process for which k1n = 387 μA/V2, k1p =86 μA/V2, Vtn =-Vtp =0.5 V, VDD =1.8 V, V1An = 5 V/μm, and V_ Ap = -6 V/μm. The output voltage must be able to swing to within approximately 0.2 V of the power-supply rails (i.e., from 0.2 V to 1.6 V), and the voltage gain must be at least 10 V/V. Design for a dc bias current of 50 μA, and use devices with the same channel length. If the channel length is an integer multiple of the minimum 0.18 μm, what channel length is needed and what W/L ratios are required? If it is required to raise the gain by a factor of 2, what channel length would be required, and by what factor does the total gate area of the circuit increase?