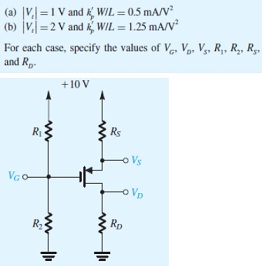

Response to the following problem:

Design the circuit in Fig. so that the transistor operates in saturation with VD biased 1 V from the edge of the triode region, with ID = 1 mA and VD = 3 V, for each of the following two devices (use a 10-μA current in the voltage divider):