Q1. Implement the following function using Actel ACT-1 logic block. Complemented inputs are not available. . F(a,b,c)= ∑(0,1,3,4,6,7);

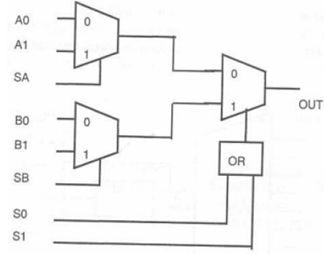

Q2. Implement the Boolean function given below using minimum number of function generators (F, G) of XC2000. Draw the K-maps for the function and write the expression.

F (a, b, c, d, e) = ∑(0, 5, 6, 9, 12, 17, 19 ,21, 27 30, 31)

Show the implementation in CLBs and mention the mode used. The implementation should be truly combinational.

Q3. Draw the PLA programming table for the following function using a PLA of a minimum size.

F1(X,Y,Z)=Σ(1,4,5,7) F2(X,Y,Z)=Σ(0,2,5,6)

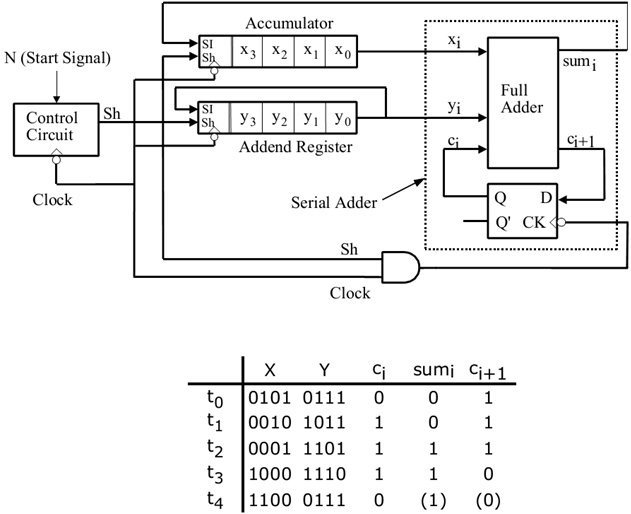

Q4. Write the verilog code for the serial adder element given below

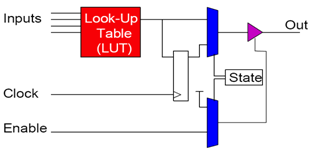

Q5. Write the verilog code for Logic element unit given below.