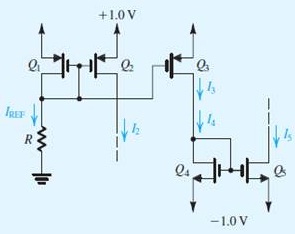

Problem:

The current-steering circuit of Figure is fabricated in a CMOS technology for which μnCox =400 μA/V2, μpCox = 100 μA/V2, Vtn = 0.5 V Vtp = -0.5 V, V_ An = 5 V/μm, and |V_ Ap | = 5 V/μm. If all devices have L = 0.5 μm, design the circuit so that IREF = 20 μA, I2 = 100 μA, I3 = I4 = 40 μA, and I5 = 80 μA. Use the minimum possible device widths needed to achieve proper operation of the current source Q2:

for voltages at its drain as high as+0.8 V and proper operation of the current sink Q5: with voltages at its drain as low as -0.8 V. Specify the widths of all devices and the value of R. Find the output resistance of the current source Q2: and the output resistance of the current sink Q5: