Response to the following problem:

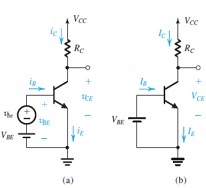

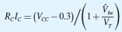

We wish to design the amplifier circuit of Figure under the constraint that VCC is fixed. Let the input signal vbe = ˆV be sin ωt, where ˆVbe is the maximum value for acceptable linearity. For the design that results in the largest signal at the collector, without the BJT leaving the active region, show that

and find an expression for the voltage gain obtained. For VCC =3 V and ˆVbe = 5 mV, find the dc voltage at the Collector, the amplitude of the output voltage signal, and the voltage gain.