Response to the following:

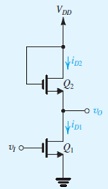

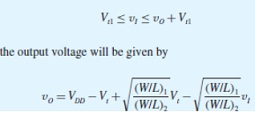

Figure shows an amplifier in which the load resistor RD has been replaced with another NMOS transistor Q2: connected as a two-terminal device. Note that because vDG of Q2: is zero, it will be operating in saturation at all times, even when vI = 0 and iD2 = iD1 = 0. Note also that the two transistors conduct equal drain currents. Using iD1 =iD2, show that for the range of vI over whichQ1: is operating in saturation, that is, for

Where we have assumed Vt1 = Vt2 = Vt . Thus the circuit functions as a linear amplifier, even for large input signals. For (W/L)1 =(50 μm/0.5 μm) and (W/L)2 =(5 μm/0.5 μm), find the voltage gain.